### ICEMOS Technology

# **Trench SOI**

#### Applications

- MEMS devices

- Solid State Relay photovoltaic generators

- Photovoltaic cells and Optoelectronic devices/ICs

- High Voltage Analog ICs for telecommunications

- High performance bipolar circuits

- Smart Power ICs

- Integrated Sensors

#### Key Features:

- Complete device isolation

- Allows significant die shrinkage compared with conventional Junction isolation

- Much lower defect density than

conventional DI technologies

- Lower Substrate capacitance than bulk

- Lower cost than trench isolation on epi

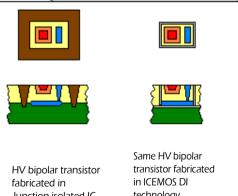

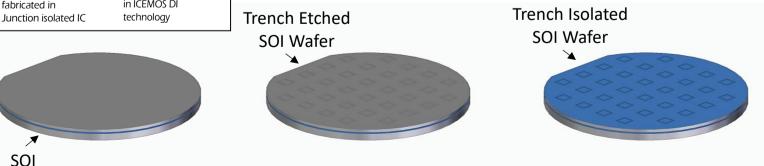

IceMOS Technology presents its dielectric isolation technology – delivering high voltage isolation between components on the same chip. Isolation is achieved using thick film SOI technology combined with state-of-the-art high aspect ratio deep trench etching and oxide/poly refill. This technology is available on all wafer sizes from 100mm to 150mm and silicon device layers from 1.5um to 100um.

#### Supply Options Available

- Provision of DI Substrate from isolation mask provided

- Provision of Fully processed DI IC using ICEMOS as foundry to complete post isolation processing

- Provision of Full IC design and fabrication on DI from customer schematic

#### Post Isolation technologies available

- Simple Bipolar

- CMOS (1P, 2M)

- BiCMOS (1P, 2M)

The IceMOS trench-isolated silicon-on-insulator (SOI) substrate provides complete dielectric isolation of tubs. Key benefits are:

- Elimination of buried layer

- Elimination of epi layer

- Elimination of P+ isolation diffusion

- Minimizing of parasitic capacitances

- High quality crystalline silicon layer

- Simultaneous increase of die per wafer

- High voltage breakdown capability

- Customised trench patterns

Our process engineers will work closely with your design group to realize the full potential for your processes.

sales@icemostech.com www.icemostech.com "Cooler than Cool"TM

IceMOS Technology Limited 5 Hannahstown Hill, Belfast, BT17 OLT +44 2890 574700

## **Trench SOI**

### **Trench SOI Specification**

| Parameter                             | Specification Range                                 |

|---------------------------------------|-----------------------------------------------------|

| Wafer Diameter                        | 100, 125, 150 mm                                    |

| Handle Layer Specifications           |                                                     |

| Handle Thickness                      | 350–800 μm                                          |

| Handle Thickness Tolerance            | ±5 μm                                               |

| Stack Thickness                       | 350–1150 μm                                         |

| Dopant Type                           | N or P                                              |

| Doping                                | N type: Phos, Red Phos, Sb & As                     |

|                                       | P type: Boron                                       |

| Resistivity                           | ≤0.001 - ≥10000 Ω-cm                                |

| Growth Method                         | CZ, MCZ or FZ                                       |

| Crystal Orientation                   | <100>, <111> or <110>                               |

| Backside Finish                       | Lapped/Etched or Polished                           |

| Buried Oxide Specifications           |                                                     |

| Thermally Oxidised Buried Oxide       | 0.2 - 4.0 µm grown on Handle, Device or both wafers |

| Thickness                             |                                                     |

| Device Layer Specifications           |                                                     |

| Device Layer Thickness                | 1.5 – 100 μm                                        |

| Tolerance                             | ± 0.5 μm                                            |

| Dopant Type                           | N or P                                              |

| Doping                                | N type: Phos, Red Phos, Sb & As                     |

|                                       | P type: Boron                                       |

| Resistivity                           | ≤0.001 - ≥10000 Ω-cm                                |

| Growth Method                         | CZ, MCZ or FZ                                       |

| Crystal Orientation                   | <100>, <111> or <110>                               |

| Buried Layer Implant                  | N type or P type                                    |

| Trench Mask Tone                      | Positive Resist                                     |

| Trench Mask Type                      | E-beam master for projection aligner                |

| Trench Line Width                     | > 2um                                               |

| Trench Aspect Ratio                   | 15:1                                                |

| Trench Sidewall Doping Type           | Phosphorus                                          |

| Trench Refill - Oxide (each sidewall) | 0.1 – 1.0 μm                                        |

| Trench Refill – Polysilicon           | To Fill (Doped or undoped Polysilicon)              |

| Planarisation                         | СМР                                                 |

| Final Field Oxide                     | Thermal oxide + TEOS up to 1um                      |

The above is a standard IceMOS specification; however, we are always happy to work with our customers to engineer specific solutions. If you would like to discuss an alternative specification, please contact our sales team: sales@icemostech.com

IceMOS Technology Limited 5 Hannahstown Hill, Belfast, BT17 OLT +44 2890 574700 sales@icemostech.com www.icemostech.com "Cooler than Cool"TM